网页设计与网站建设大作业怎么去推广自己的店铺

目录

- 1.计算机存储层次结构

- 2.缓存相关概念

- 3.缓存组织方式

- 4.Cache回写机制

- 5.Cache性能量化

1.计算机存储层次结构

计算机存储层次结构可以看作是一个金字塔,越靠上层,容量越小,速度越快

- L0:寄存器----CPU的寄存器保存着Cache取出的字,你要玩过单片机对这个肯定不陌生

- L1:高速缓存SRAM----L1中保存着L2取出的缓存行

- L2:高速缓存SRAM----L2中保存着L3取出的缓存行

- L3:高速缓存SRAM----L3中保存着主存中取出的缓存行,L1-L3也就是我们常说的三级缓存,用的都是SRAM芯片实现,速度快

- L4:主存DRAM----主存保存着从本地磁盘取出的磁盘块,用的是DRAM芯片实现

- L5:本地磁盘----保存着从远程网络或者服务器磁盘上取出的文件

- L6:远程二级存储----如web服务器

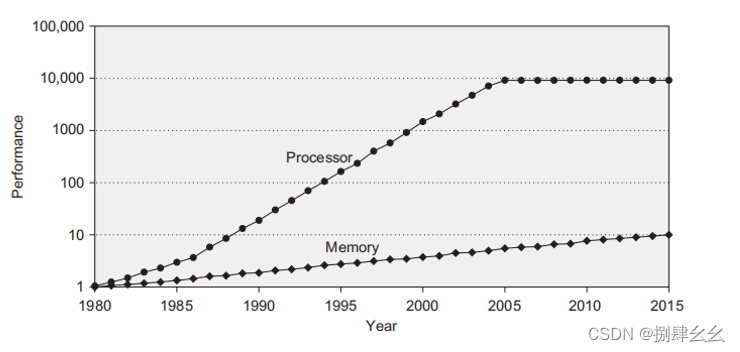

那为什么需要缓存呢?我看下面的一张图,此图说明了处理器的性能发展远远比内存性能的发展要快,而处理器访问内存的速度会因为性能差太大而降低,因此出现了高速缓存Cache

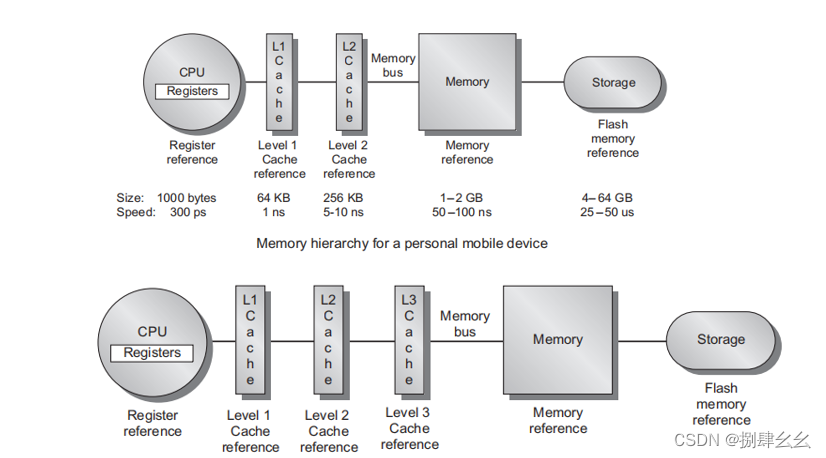

往常的PMD(个人移动设备)的存储结构如下图,都是通过CPU+Cache+Memory+Flash的形式,层级传递

2.缓存相关概念

- 缓存命中----当程序需要在底层次的存储原件里面的数据的时候,发现在比它高层次的存储原件中存在数据,那么程序就不用去访问底层次的存储原件,直接访问高层次的原件,这就叫缓存命中。举个例子:当CPU想获得L4层的主存中的某数据s,却发现在L2Cache有数据s,这就可以直接访问快速的L2层取得数据,这就是缓存命中。

- 缓存不命中:高层中没有想要的数据,只能替换和驱逐高层次的一些块,再去访问。

- 缓存不命中/缺失的三种种类 (1)强制缺失:第一次访问缓存必定不命中,因为第一次缓存里面是空的(2)容量缺失:缓存不能包含程序运行期间所需要的全部块,容量已经满了(3)冲突缺失:多个块映射到一个块中的组中,明明有空位给你缓存你却不要去空位,偏要挤出其他块。

3.缓存组织方式

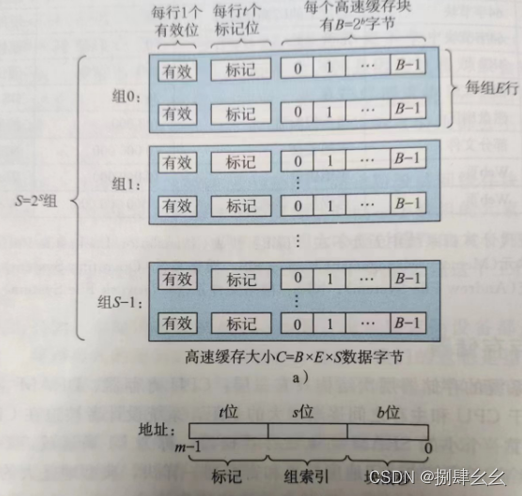

高速缓存一般被组织成这样的情形:

①高速缓存分为若干个组

②组又分为若干个行

③行包含了数据块、有效位、标记位

④可以用向量(S,E,B,m)来表示高速缓存的组织情况

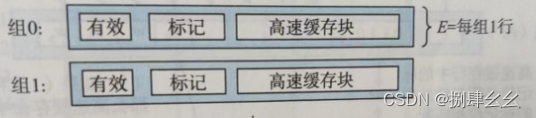

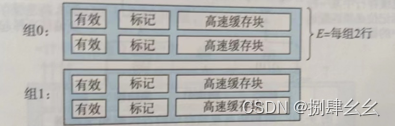

- 直接相联高速缓存:根据每个组的高速缓存行数E, 高速缓存被分为不同的类。每个组只有一行(E = 1)的高速缓存称为直接映射高速缓存。

- 组相联高速缓存:直接映射高速缓存很容易出现冲突不命中的情况,因为每个组只有一行。组相联高速缓存放松了这条限制,所以每个组都保存有多于一个的高速缓存行。一个1<E<C/B的高速缓存通常称为E路组相联高速缓存。

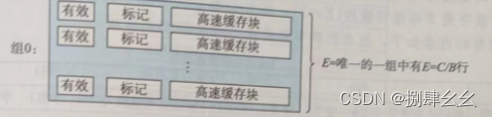

- 全相联高速缓存:全相联高速缓存是由一个包含所有高速缓存行的组组成的(只有一个组)

4.Cache回写机制

①两种写入策略

- 写直达:信息被写入缓存的过程中同时写入低一级的存储器的块

- 写回:信息被写入缓存,只有块被替换踢掉的时候才被写回低一级存储器进行更新

②两种写的比较

- 写直达虽然占了很多带宽(通过写缓冲区减少停顿),但是保持了数据一致性,缓存永远是最新的

- 写回策略少带宽,节省功耗,但是在一致性方面有点问题

③写缺失时采用的两种策略

- 写分配:如果写缺失,把写缺失的块缓存进来,然后再进行写命中时的操作(通常跟写回搭配)

- 非写分配:直接修改低一级的存储器(通常跟写直达搭配)

其实说白了还是要保证Cache一致性的问题

5.Cache性能量化

①一些概念

- 缺失率:一次访问存储器缺失的概率

- 缺失数:一条指令缺失的概率

- 相互关系:缺失数 = 缺失率*存储器访问指令数在指令数的占比(IC)

- 命中时间:缓存命中的时间

- 缺失代价:将块从存储器读取到缓存所需要的时间

②重要公式

存储器的平均访问时间 = 命中时间 + 缺失率 * 缺失代价

③6个基本优化方案

根据上述公式提出优化方案:

- 增大块的大小降低缺失率(可能增加冲突缺失,到后面会增加缺失率,也可能增加缺失代价)

- 增大缓存以降低缺失率(延长命中时间,一般采用在片外缓存)

- 提高相联度以降低缺失率(减小冲突缺失,但会延长命中时间)

- 采用多级缓存降低缺失代价(市面处理器基本上就是多级缓存)

- 使读缺失的优先级高于写缺失,以降低缺失代价

- 避免索引期间进行地址转换,以缩短命中时间(跟虚拟内存相关)